There are two methods of sampling, by time period or bit state.

The following shows the execution conditions for the Sampling, and the characteristic of each action.

Time Period

|

Sampling Execution Condition |

Attribute |

|

Set Time Sampling begins at the designated time and continues for the designated period. |

|

|

Constant Cycle*2 Sample data at constant cycles starting from when the display unit is turned ON. |

|

|

Constant Cycle when Bit is ON*2 Sample data at constant cycles starting from when the display unit is turned ON, but only when the designated bit is ON. |

|

Bit

|

Sampling Execution Condition |

Attribute |

|

Bit ON Data is collected every time the designated bit turns ON. |

|

|

Bit Change*2 Data is collected every time the designated bit changes state (ON/OFF). |

|

*1 A group of sampling data over a specified number of times is called a "Block".

![]() 25.14.3.2 Data Storage Methods

25.14.3.2 Data Storage Methods

*2 When using [Constant Cycle], [Constant Cycle while Bit is ON], or [Bit Change], the moment the Execution Condition is satisfied, reads data from all the defined addresses and saves the data to the display unit.

![]()

After the display unit is powered ON and the internal programs are prepared, one second maximum of delay time may occur before the sampling starts.

When using [Constant Cycle], [Constant Cycle while Bit is ON], or [Bit Change], after powering up these sampling groups read in data for all the defined addresses before starting sampling operations.

For [Constant Cycle], [Constant Cycle when Bit is ON], and [Bit Change], because all the set address data is being read, the communication may put a burden on the system if the number of addresses to sample is large.

The data's display state when a communication error occurs during sampling depends on the execution condition.![]() 25.14.4.3 If data cannot be sampled

25.14.4.3 If data cannot be sampled

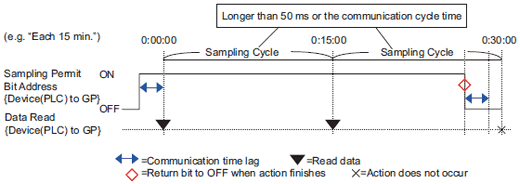

When a device/PLC [Sampling Permit Bit Address] is ON and the designated [Start Time] begins, the data from the designated addresses is read. After that, the data is read at the designated cycle.

The sampling cycle's time monitor is operated by the display unit's internal clock.

![]()

The above image shows the timing of the display unit reading data from the designated address. It doesn't show accurate time intervals.

Please set the [Sampling Cycle] to either the communication cycle time or the time taken to communicate/read the data, whichever is longer. Communication cycle time is stored in the internal device's (Special Relay Area) LS2037 of display unit.

After the start time, when the Sampling Permit Bit Address is set ON, any data before the start time becomes a read error.![]() 25.14.4.3 If data cannot be sampled

25.14.4.3 If data cannot be sampled

Read errors are recorded when the Sampling Permit Bit Address is turned ON and there is no sampling data.

If sampling data exists, and the Sampling Permit Bit Address is turned ON, samples are stored on the next sample.

Sampled data will also have the sample time added to it. The start time of the data read at the designated [Start Time] and each [Sampling Cycle] will become the "time data".

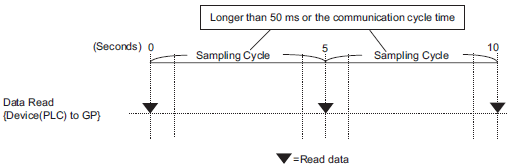

Constant Cycle

Read data at the designated fixed cycle starting from when the display unit is turned ON.

The sampling cycle's time monitor is operated by the display unit's internal clock.

![]()

The above image shows the timing of the display unit reading data from the designated address. It doesn't show accurate time intervals.

If the time is adjusted in the middle of sampling, it will cause a maximum discrepancy of one second in the sampling time.

When using the Direct Access method to communicate with the device/PLC, set the [Sampling Cycle] to the communication cycle time or 50 ms, whichever is longer. For the Memory Link method, set the [Sampling Cycle] to 50 ms or more. Communication cycle time is stored in the internal device's (Special Relay Area) LS2037 of display unit.

Constant Cycle when Bit is ON

When the device/PLC [Sampling Trigger Bit Address] is ON, data is read at the designated cycle. The sampling cycle time is monitored by the display unit's internal clock.

![]()

The above image shows the timing of the display unit reading data from the designated address. It doesn't show accurate time intervals.

The time period from when the [Sampling Permit Bit Address] turns ON to the time the sampling actually begins can be up to one second.

If the time is adjusted in the middle of sampling, it will cause a maximum discrepancy of one second in the sampling time.

When using the Direct Access method to communicate with the device/PLC, set the [Sampling Cycle] to the communication cycle time or 50 ms, whichever is longer. For the Memory Link method, set the [Sampling Cycle] to 50 ms or more. Communication cycle time is stored in the internal device's (Special Relay Area) LS2037 of display unit.

Please ensure that each bit address such as the [Sampling Trigger Bit Address] and [Data Full Bit Address] is in the OFF state when power is turned ON in case the display unit's power is turned OFF while an action is running,

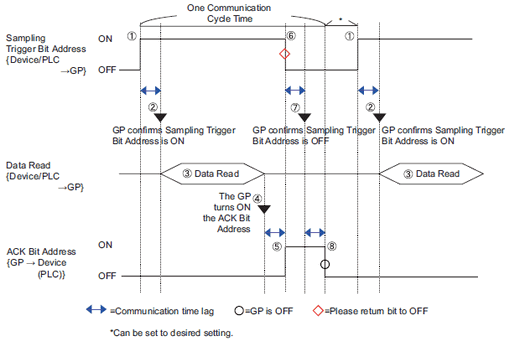

When the device/PLC [Sampling Trigger Bit Address] turns ON, the designated address data is read to the display unit. When the display unit finishes reading data, the [ACK Bit Address] is turned ON.

When you detect that the device/PLC [ACK Bit Address] has turned ON, please turn OFF the [Sampling Trigger Bit Address]. When you turn OFF the [Sampling Trigger Bit Address], the [ACK Bit Address] will be automatically turned OFF.

![]()

The above image shows the timing of the display unit reading data from the designated address. It doesn't show accurate time intervals.

Please plan the action settings to take into consideration cases where the GP's power is turned OFF while an action is running.

Please ensure that each bit address such as the [Sampling Trigger Bit Address] and [ACK Bit Address] is in the OFF state when power is turned ON in case the display unit's power is turned OFF while an action is running.

When adding the acquisition time (time data) to sampling data, the time data is not the time when [Sampling Trigger Bit Address] is ON, but the time when the data reading is completed.

The [Sampling Trigger Bit Address] will not function correctly if turned OFF immediately after being turned ON. Please wait until the display unit can recognize the bit state as ON or OFF. (When using the Direct Access method, the wait time should be the communication cycle time or 50 ms, whichever is longer. For the Memory Link method, 50 ms or more.)

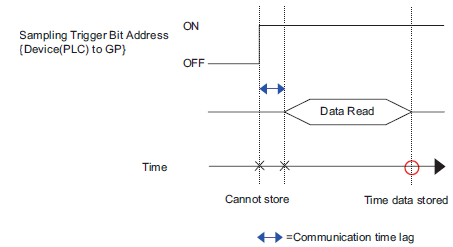

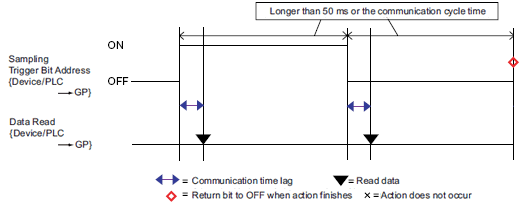

Bit Change

When the device/PLC [Sampling Trigger Bit Address] turns ON or OFF, the designated address data is read to the display unit.

![]()

The above image shows the timing of the display unit reading data from the designated address. It doesn't show accurate time intervals.

Please ensure that each bit address such as the [Sampling Trigger Bit Address] and [Data Full Bit Address] is in the OFF state when power is turned ON in case the display unit's power is turned OFF while an action is running.

The [Sampling Trigger Bit Address] will not function correctly if turned OFF immediately after being turned ON. Please wait until the display unit can recognize the bit state as ON or OFF. (When using the Direct Access method, the wait time should be the communication cycle time or 50 ms, whichever is longer. For the Memory Link method, 50 ms or more.)